Двухтактный триггер – —

D-триггеры.

Интегральным D-триггером называется триггер с одним сигнальным и одним тактовым входом.

Такие триггеры носят другое название — триггер задержки. Название произошло от английского слова delay (задержка).

D-триггеры предназначены для выполнения следующих основных операций:

запоминание информации;

задержка логических сигналов;

счет поступающих импульсов.

D-триггеры являются синхронными триггерами и классифицируются по количеству тактов работы

Рассмотрим указанные выше основные схемы D-триггеров.

Однотактный d- Триггер

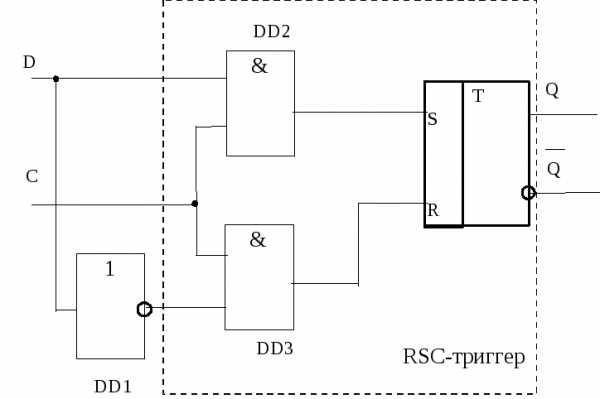

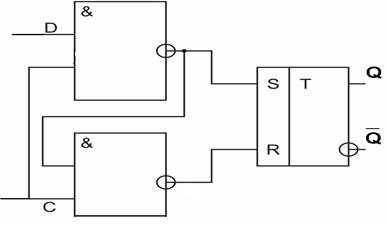

Однотактный D— триггер состоит из синхронного RSC-триггера, дополненного инвертором.

Условное обозначение однотактного D- триггера имеет следующий вид.

Рис. 0.16Принцип действия- однотактного D- триггера заключается в следующем:

Любой сигнал на D входах создает на RS входах взаимно инвертированную комбинацию (S=0, R=1 или R=0, S=1).

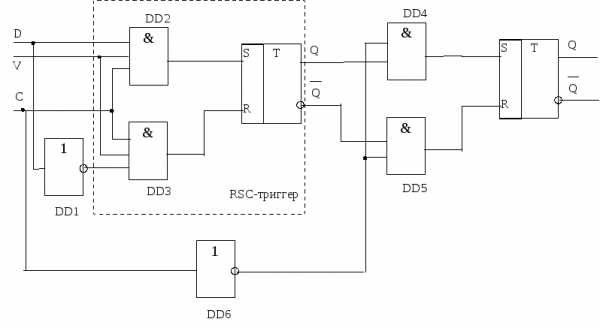

Схема однотактного D- триггера имеет вид представленный ниже.

Рис. 0.17

Работу однотактного D- триггера рассмотрим в двух случаях:

при подаче на синхронизирующий вход С логической единицы;

подаче на синхронизирующий вход С логического нуля.

Рассмотрим указанные случаи по порядку.

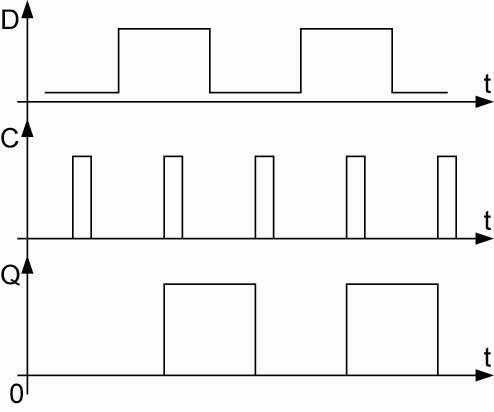

При подаче на вход С ”1” значение сигнала, поступающего на D-вход через элемент DD2 подается на S вход триггера Т1. В этом случае S=D, а на входе R сигнал инвертированный по сравнению с сигналом на входе D, т.е. R=. Таким образом, сигналы на S- и R- входах являются взаимно инвертированными благодаря элемента ИЛИ — НЕ DD1. В результате любой сигнал на D-входе создает комбинацию S=1, R=0 или S=0, R=1. При этом триггер переключается в состояние Q=S=D. Таким образом, при С=1 D — триггер на выходе Q повторяет потенциал D -входа с задержкой относительно сменившегося потенциала входа С (поступления тактовых импульсов).

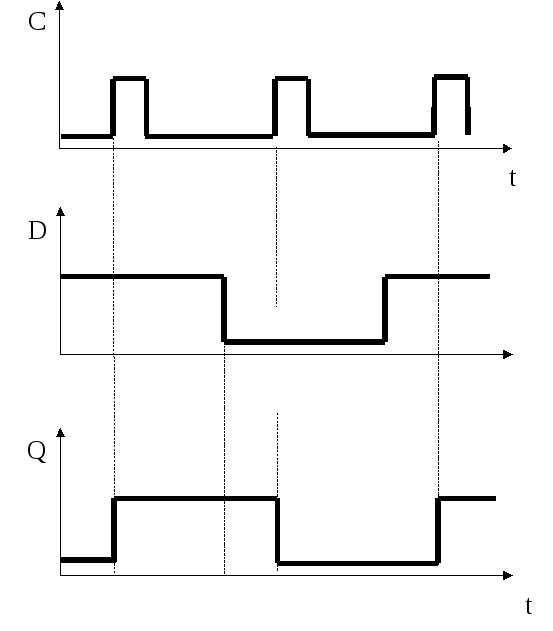

При подаче на вход С “0” за счет элементов И DD2 и DD3 сигналы на входах S и R равны нулю. Триггер хранит предыдущую информацию. Т.е. в этом случае нулевой сигнал на D входе на состояние триггера не влияет и он хранит информацию, поступившую когда на входе С была “1”. Таким образом, работу схемы можно пояснить диаграммой.

Рис. 0.18

Dv –Триггер

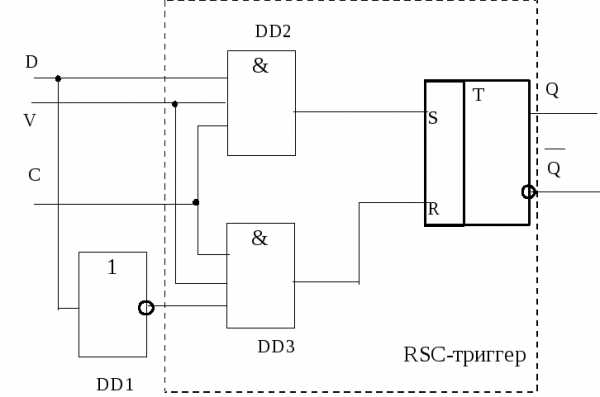

Введение ещё одного дополнительного входа (valve клапан) позволяет реализовать универсальный триггер DV типа.

Условное обозначение DV –триггера:

Схема DV -триггера имеет вид.

Рис. 0.20

Работа DV -триггера происходит следующим образом.

При V=1 триггер функционирует, как D-триггер.

При V=0 на входах S и R присутствует логический ноль независимо от того какой сигнал поступает на входы D и С.

Таким образом, как видим, информационный вход отключается от триггера. Т.е. триггер блокируется. Его состояние остается таким, каким оно было до момента поступления на вход V нуля и не зависит от смены сигналов на D-входе.

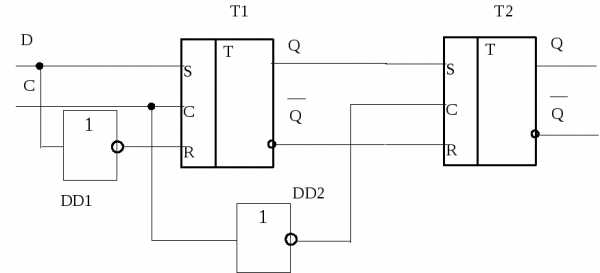

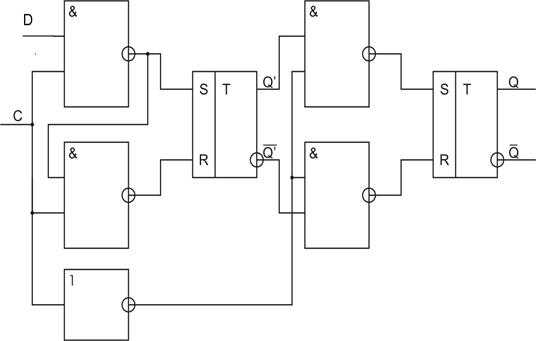

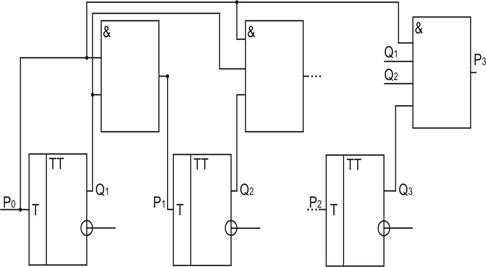

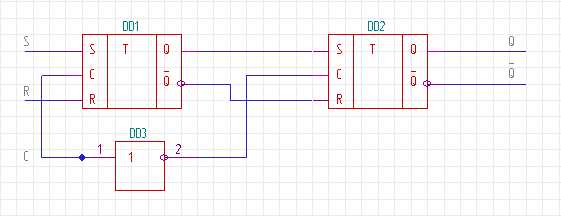

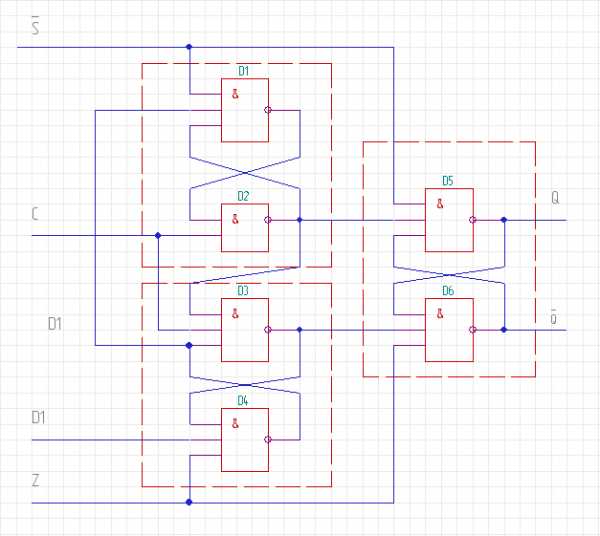

Двухтактный ( двухступенчатый) d-триггер

D — триггер можно выполнить двухступенчатым.

Первая ступень представляет собой одноступенчатый D-триггер, а вторая — синхронный RS-триггер.

На схемах двухтактный D- триггер обозначается следующим образом.

Рис. 0.21

Принцип действия двухтактного D- триггера основан на принципе действия RS триггера с динамическими входами. Т.е. первая ступень переключается по переднему фронту тактового импульса, вторая по его срезу.

Схема двухтактного D- триггера имеет следующий вид.

Рис. 0.22

Работа двухтактного D- триггера наглядно отражена в описании его принципа работы

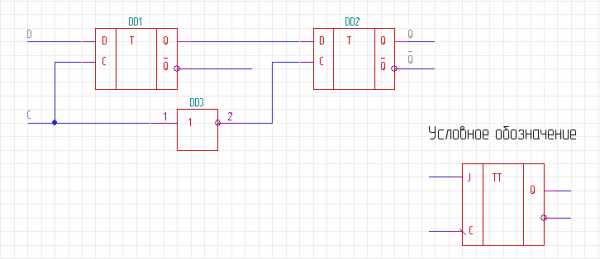

Так же как и в одноступенчатом Dтриггере в 2-х ступенчатой схеме возможно реализовать функцию valve. В результате получим универсальный 2-х ступенчатый DV-триггер.

Рис. 0.23

Условное обозначение такого триггера имеет следующий вид:

Рис. 0.24

Двухступенчатый D-триггер получил широкое применение из-за его универсальности. Так, например, если соединить с D входом, то с каждым синхроимпульсом будет меняться потенциал на входе D и, следовательно, состояние триггера. Таким образом, получается счетный Т-триггер.

Рис. 0.25

Кроме того, на базе таких триггеров можно реализовать и другие виды триггеров.

Развитие универсальных триггеров происходит в связи с необходимостью экономии средств при проектировании и изготовлении радиоэлектронной аппаратуры.

Реальные микросхемы функционально являющиеся D -триггерами обозначаются следующим образом: ТМ. Так, например, микросхема 155ТМ2 является D-триггером.

Итак Dтриггеры, цифровые устройства со счётным запуском, и не имеющие запрещённых комбинаций сигналов, подаваемых на их информационные входы.

studfile.net

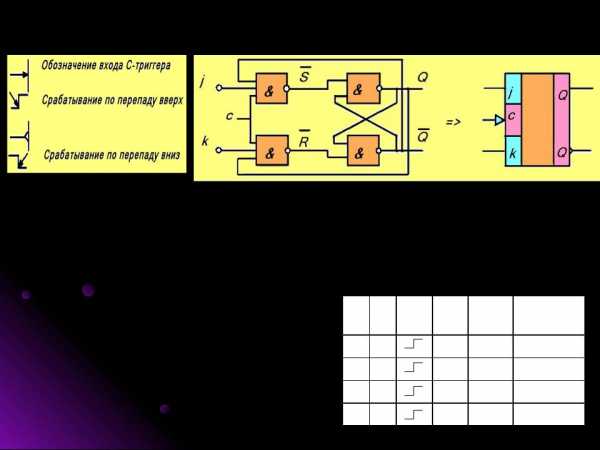

• Однотактные и двухтактные триггеры

Рис. Однотактный JK триггер и его словное обозначение

Срабатывает в момент перехода строб сигнала С с 0 в 1(по его переднему фронту).

Таблица состояний однотактног jk -триггера

•Если соединить входы j,с и k, то получится Т-триггер.

•Если с = 0, то хранение при любых J и K.

•В jk триггере запрещенных состояний нет

|

|

|

|

| состояние |

Jn | Kn C | Qn+1 | Qn 1 | ||

|

|

| |||

0 | 0 | Qn | Qn | хранение | |

0 | 1 | 0 | 1 |

| запись 0 |

1 | 0 | 1 | 0 |

| запись 1 |

1 | 1 | Qn | Qn | Т–триггер | |

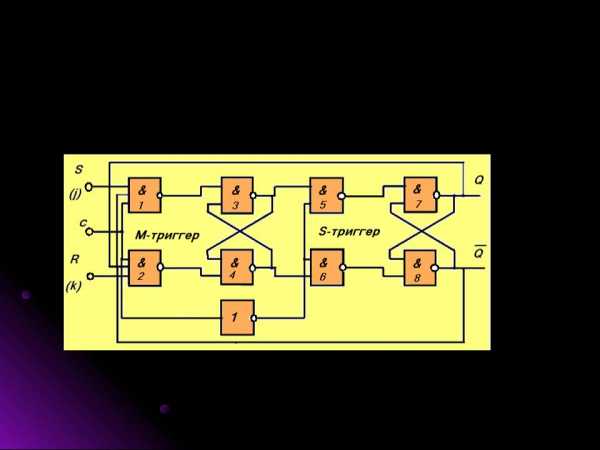

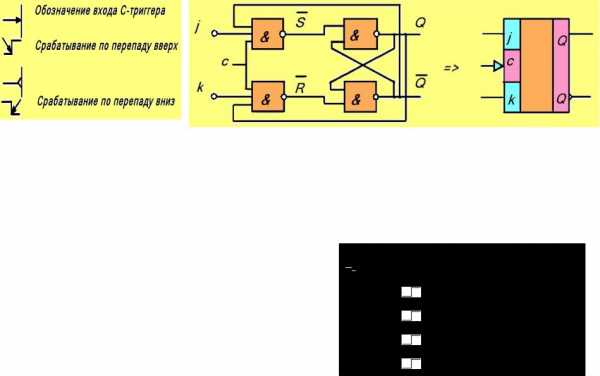

Двухтактные (2х ступенчатые) триггеры

1) Двухтактный RS-триггер (MS-триггер)

При С = 1, информация принимается в М триггер, но не проходит в S-триггер.

При С = 0, информация из М-триггера переписывается в S-триггер.

ведущий | ведомый |

При любом С | одна ступень триггера“прозрачна”, другая |

“непрозрачна”, поэтому триггер в целом непрозрачен.

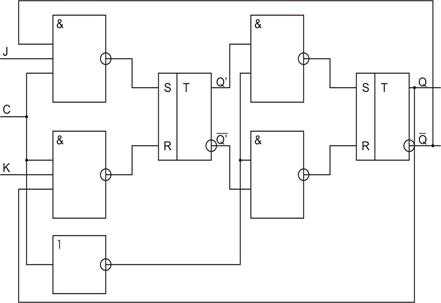

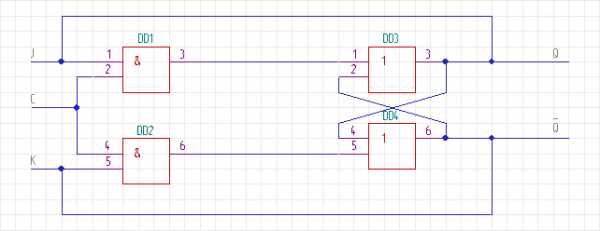

•Двухтактный JK-триггер

Это двухтактный RS-триггер, выходы Q которого заведены накрест на входные конъюнкторы тогда R и S входы называются J и К входами.

Если j = k = 0 то С-сигнал не может открыть триггер – хранение.

Если j = 1; k = 0 ,то С-сигнал откроет конъюнктор &1, но только если до поступления С- сигнала было: Q = 0;

•В отличие от обычного RS-триггера, вариант j = k = 1 не запрещён.

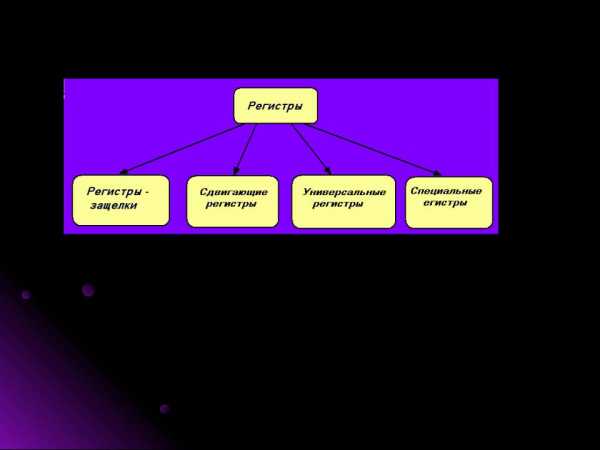

ТЕМА 12. Регистры.

Классификация регистров.

Параллельные и последовательные регистры.

Парафазные и однофазные регистры.

Сдвигающие регистры.

Регистр – функциональный узел объединяющий несколько

однотипных триггеров

Типы регистров:

Регистры защелки – строятся на триггерах защелках (К155ТМ5; К155ТМ7),запись в которые ведется уровнем стробирующего сигнала.

В триггере К155ТМ8 – запись ведется положительным фронтом стробирующего сигнала.

Сдвигающие регистры – выполняют функцию только последовательного приема кода.

Универсальные регистры – могут принимать информацию в параллельном и последовательном коде.

Специальные регистры – К589ИР12 имеют дополнительные

варианты использования.

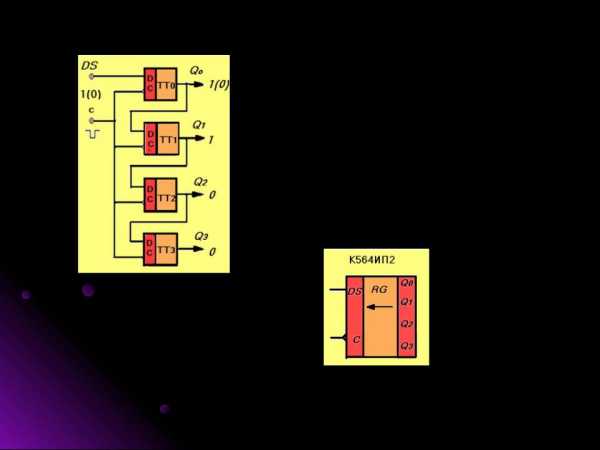

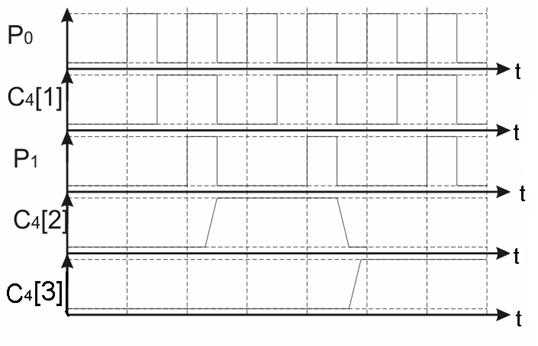

•Сдвигающий регистр

Это регистр, содержимое которого при подаче управляющего сигнала может сдвигаться в сторону старших или младших разрядов. Например, сдвиг влево приведен в таблице 9.

Таблица 9 Сдвиг кода влево

0 | 1 | 1 | 0 |

1 | 1 | 0 | 0 |

1 | 0 | 0 | 0 |

0 | 0 | 0 | 0 |

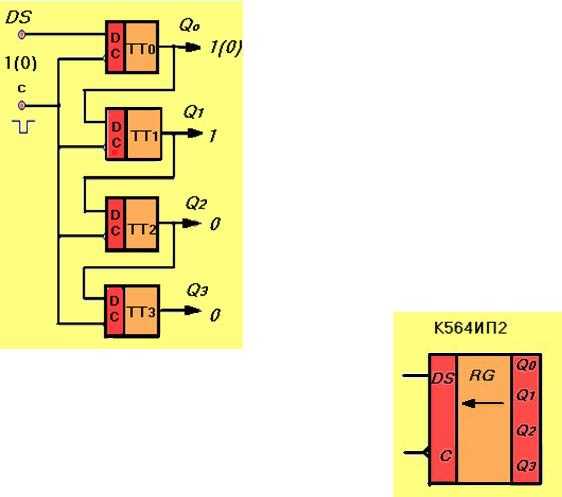

•Регистр с однофазной синхронизацией.

В регистр с однофазной синхронизацией в момент поступления стробирующего импульса происходит запись входного бита DS в триггерТТ0.В триггер ТТ1 переписывается информация имевшаяся ТТ0, в ТТ2 из ТТ1 и т.д.

На вход DS поступает последовательный код.

•При подаче следующего бита DS и сигнала С происходит тот же процесс, в результате все биты имевшиеся на выходах Q0-Q3 передвигаются на 1 разряд влево. Условное обозначение такого регистра приведено на рисунке

Условное обозначение

•Сдвиговый регистр (условное обозначение)

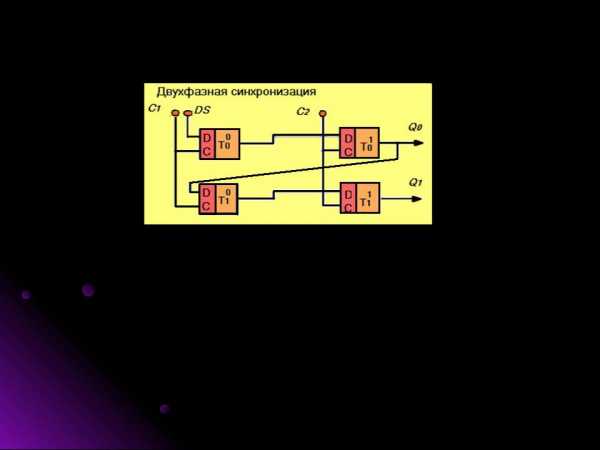

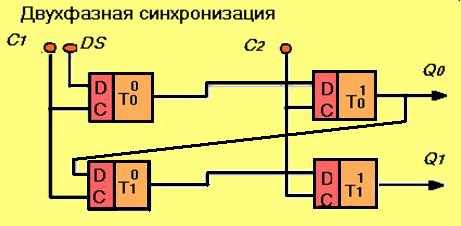

Двухфазный сдвиговый регистр

Вдвухфазном регистре по сигналу С1 происходит запись в однотактные триггеры Т00 и Т01, а по сигналу С2 информация переписывается в триггеры Т10 и Т11 и появляется на выходах Q0 и Q1. Сдвиговые регистры применяются для преобразования последовательного кода в параллельный.

Тема 13. Счетчики

Классификация счетчиков.

Синтез счетчиков.

Двоичные счетчики.

Счетчики с переменным модулем счета.

Суммирующие, вычитающие и

реверсивные счетчики

•Классификация счетчиков

Счетчик — функциональный узел предназначенный для счета

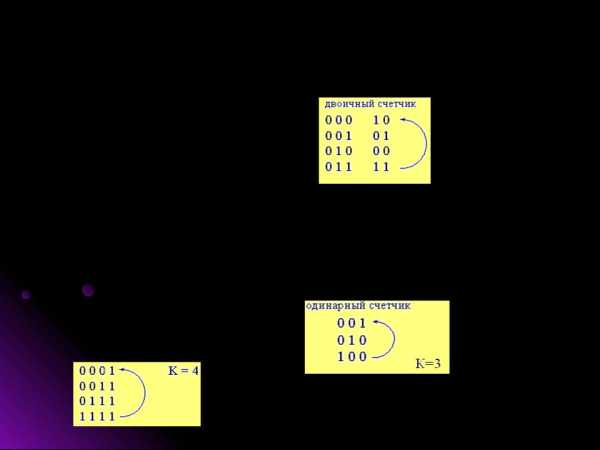

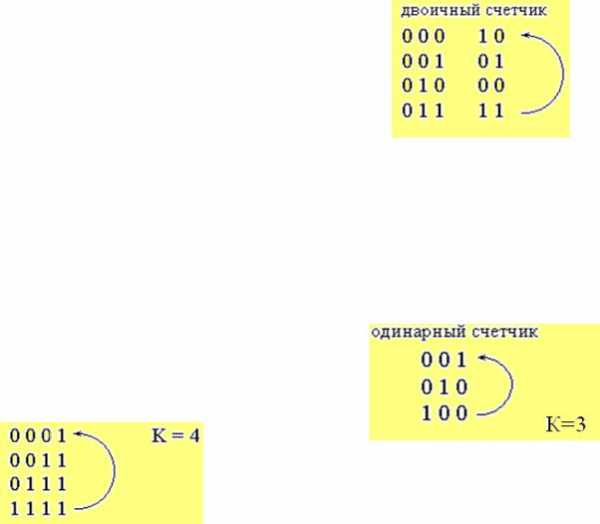

сигналов. По мере поступления входных сигналов счетчик последовательно перебирает свои состояния в определенном для данной схемы порядке. Например:

•Длина списка используемых состояний К называется модулем пересчета или емкостью счетчика.

•Наиболее часто используются двоичные счетчики, у которых порядок смены

состояний триггеров соответствует последовательности двоичных кодов.

•Применяются и другие виды кодирования, например одинарное, когда состояние счетчика определяется местоположением движущейся единицы.

•Унитарное кодирование – состояние

определяется числом единиц

studfile.net

• Однотактные и двухтактные триггеры

Рис. Однотактный JK триггер и его словное обозначение

•Срабатывает в момент перехода строб сигнала С с 0 в 1(по его переднему фронту).

Таблица состояний однотактног jk -триггера

•Если соединить входы j,с и k, то получится Т-триггер.

•Если с = 0, то хранение при любых J и K.

•В jk триггере запрещенных состояний нет

|

|

|

|

| состояние |

Jn | Kn C | Qn+1 | Qn 1 | ||

|

|

| |||

0 | 0 | Qn | Qn | хранение | |

0 | 1 | 0 | 1 |

| запись 0 |

1 | 0 | 1 | 0 |

| запись 1 |

1 | 1 | Qn | Qn | Т–триггер | |

Двухтактные (2х ступенчатые) триггеры

1)Двухтактный RS-триггер (MS-триггер)

При С = 1, информация принимается в М триггер, но не проходит в S-триггер.

При С = 0, информация из М-триггера переписывается в S-триггер.

ведущий | ведомый |

При любом С | одна ступень триггера“прозрачна”, другая |

“непрозрачна”, поэтому триггер в целом непрозрачен.

•Двухтактный JK-триггер

Это двухтактный RS-триггер, выходы Q которого заведены накрест на входные конъюнкторы тогда R и S входы называются J и К входами.

Если j = k = 0 то С-сигнал не может открыть триггер – хранение.

Если j = 1; k = 0 ,то С-сигнал откроет конъюнктор &1, но только если до поступления С- сигнала было: Q = 0;

•В отличие от обычного RS-триггера, вариант j = k = 1 не запрещён.

ТЕМА 2. Регистры.

Классификация регистров.

Параллельные и последовательные регистры.

Парафазные и однофазные регистры. Сдвигающие регистры.

Регистр – функциональный узел объединяющий несколько

однотипных триггеров

•Типы регистров:

•Регистры защелки – строятся на триггерах защелках (К155ТМ5; К155ТМ7),запись в которые ведется уровнем стробирующего сигнала.

•В триггере К155ТМ8 – запись ведется положительным фронтом стробирующего сигнала.

•Сдвигающие регистры – выполняют функцию только последовательного приема кода.

•Универсальные регистры – могут принимать информацию в параллельном и последовательном коде.

•Специальные регистры – К589ИР12 имеют дополнительные

•варианты использования.

•Сдвигающий регистр

•Это регистр, содержимое которого при подаче управляющего сигнала может сдвигаться в сторону старших или младших разрядов. Например, сдвиг влево приведен в таблице 9.

Таблица 9 Сдвиг кода влево

0 | 1 | 1 | 0 |

1 | 1 | 0 | 0 |

1 | 0 | 0 | 0 |

0 | 0 | 0 | 0 |

•Регистр с однофазной синхронизацией.

В регистр с однофазной синхронизацией в момент поступления стробирующего импульса происходит запись входного бита DS в триггерТТ0.В триггер ТТ1 переписывается информация имевшаяся ТТ0, в ТТ2 из ТТ1 и т.д.

• На вход DS поступает последовательный код.

•При подаче следующего бита DS и сигнала С происходит тот же процесс, в результате все биты имевшиеся на выходах Q0-Q3 передвигаются на 1 разряд влево. Условное обозначение такого регистра приведено на рисунке

Условное обозначение

Сдвиговый регистр (условное обозначение)

•Двухфазный сдвиговый регистр

Вдвухфазном регистре по сигналу С1 происходит запись в однотактные триггеры Т00 и Т01, а по сигналу С2 информация переписывается в триггеры Т10 и Т11 и появляется на выходах Q0 и Q1. Сдвиговые регистры применяются для преобразования последовательного кода в параллельный.

Тема 3. Счетчики

Классификация счетчиков. Синтез счетчиков. Двоичные счетчики.

Счетчики с переменным модулем счета.

Суммирующие, вычитающие и реверсивные счетчики

•Классификация счетчиков

•Счетчик — функциональный узел предназначенный для счета

сигналов. По мере поступления входных сигналов счетчик последовательно перебирает свои состояния в определенном для данной схемы порядке. Например:

•Длина списка используемых состояний К называется модулем пересчета или емкостью счетчика.

•Наиболее часто используются двоичные счетчики, у которых порядок смены

состояний триггеров соответствует последовательности двоичных кодов.

•Применяются и другие виды кодирования, например одинарное, когда состояние счетчика определяется местоположением движущейся единицы.

•Унитарное кодирование – состояние

определяется числом единиц

studfiles.net

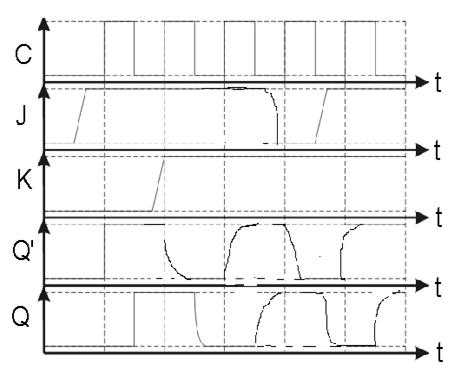

Триггер со счетным входом (Т–триггер)

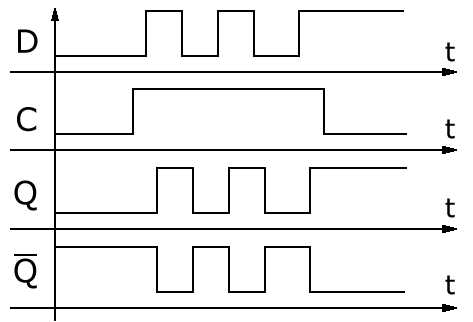

⇐ ПредыдущаяСтр 2 из 4Следующая ⇒Основной особенностью Т-триггера является то, что при поступлении на его вход очередного импульса триггер изменяет свое состояние на противоположное. Существуют две структуры Т–триггеров: однотактная и двухтактная. Однотактные схемы в настоящее время практически не используются из-за их недостаточной надежности.

На рис. 8.7 представлена логическая схема Т-триггера со счетным входом, построенная на элементной базе “И-ИЛИ-НЕ”. Как видно из схемы, выходы триггера Q связаны со входами обратными связями.

Рис. 8.7. Логическая схема двухтактного Т- триггера

Двухтактная схема используется для того, чтобы с помощью обратной связи создать механизм запоминания предыдущего состояния триггера на время переходного процесса при установке триггера первой ступени в противоположное состояние.

УГО Т-триггера показано на рис. 8.9. Как видно из временной диаграммы (рис.8.8), при поступлении очередного импульса на счетный вход триггера его состояние меняется на противо-положное. При этом между моментами срабатывания триггеров первой и второй ступеней имеется временная задержка, равная длительности синхроимпульса. Частота импульсов, поступающих на вход триггера, делится на два, т.е. сам триггер срабатывает в 2 раза реже.

Рис. 8.8. Временная диаграмма работы Т-триггера

Рис.8.9. УГО Т- триггера

Таблица 8.2

| Сt | Q1t+0,5 | Qt+1 |

| Q1t | Qt | |

| ┐Qt | ┐Qt |

В табл. 8.2 представлена таблица переходов триггера со счетным входом. В ней символ “ ┐” обозначает инверсию сигнала Q.

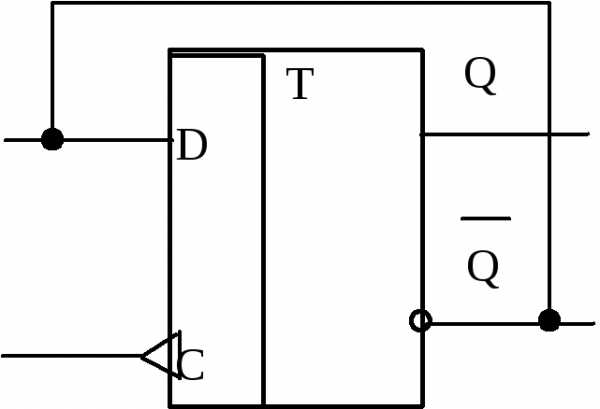

Универсальный D-триггер (триггер-задержка)

Его особенность в том, что он имеет один информационный вход (название D от Delay). Триггер запоминает (задерживает) информацию, которая поступает по одному информационному каналу. Триггер также называется универсальным, так как на его основе можно построить все другие типы триггеров. Существуют две структуры D-триггера: однотактная и двухтактная.

8.3.1. Однотактный D-триггер

На рис. 8.10 показано УГО однотактного D –триггера. На рис.8.11 представлена логическая схема D -триггера, построенная на ЛЭ типа “ И-НЕ”. Особенность этой схемы состоит в том, что имеется только один информационный вход D.

Рис. 8. 10. УГО однотактного D-триггера

Рис. 8.11. Логическая схема однотактного D-триггера

Таблица 8.3

В табл. 8.3 дана таблица переходов однотактного D-триггера.

Из этой таблицы видно, что при С =1 на выходе триггера устанавливается состояние, равное значению входа D.

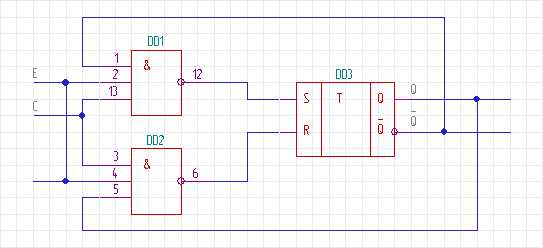

Двухтактный D-триггер

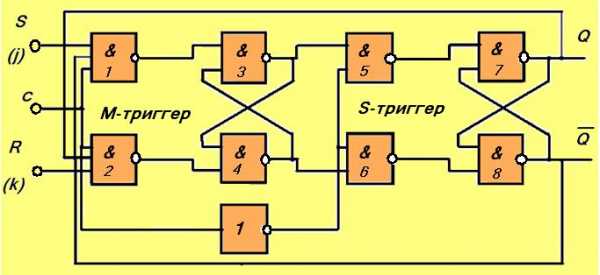

На рис. 8.12 представлена логическая схема двухтактного D -триггера, построенного на элементной базе “И-НЕ”. УГО двухтактного D –триггера представлено на рис. 8.13. Эта схема отличается от двухтактного R-S -триггера тем, что у нее только один информационный вход D.

Рис. 8.12. Логическая схема двухтактного D-триггера

Рис. 8.13. УГО двухтактного D-триггера

Рис.8.14. Т-триггер на основе двухтактного D-триггера

На основе двухтактного D-триггера можно построить Т-триггер, при этом роль счетного входа выполняет вход С (рис.8.14).

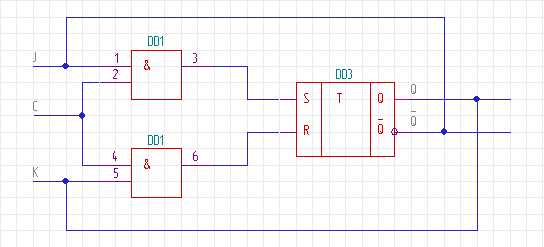

Универсальный JK-триггер

Эта схема называется универсальной потому, что на ее основе можно построить все основные типы триггеров. JK-триггер имеет только двухтактную структуру (рис.8.15). УГО JK –триггера изображено на рис.8.16.

Рис. 8.15. Логическая схема JK –триггера

Рис. 8.16. УГО JK –триггера

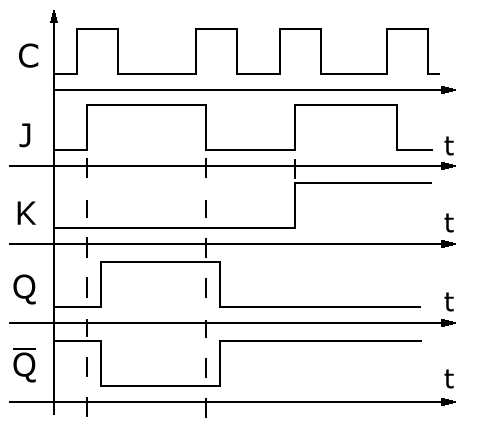

Рис. 8.17. Временная диаграмма работы JK –триггера

На рис. 8.15 представлена логическая схема JK –триггера, которая представляет собой двухступенчатую структуру с обратными связями. Так как схема собрана на ЛЭ “И-НЕ”, то в таблице переходов (табл. 8.4) работа триггера рассматривается в условиях положительной логики. Вход J является входом установки в состояние “1” , вход K – входом установки в “0”.

Триггер первой ступени срабатывает по положительному фронту синхроимпульса, а триггер второй ступени управляется инвертированным синхроимпульсом, т.е. срабатывает по отрицательному фронту синхроимпульса через 0.5 такта.

Рассмотрим работу триггера, используя временную диаграмму (рис.8.17). В первом такте синхроимпульс С:=0, оба триггера находятся в нулевом состоянии. Во втором такте C:=1,K:=0, J: =1 и положительным фронтом синхроимпульса уста-

навливается триггер Q’:=1, а затем через 0,5 такта по заднему фронту это состояние передается во второй триггер Q: =1.

Таблица 8.4

| Ct | J | K | Qt+0,5 | Qt+1 |

| x | x | Qt’ | Qt | |

| Qt’ | Qt | |||

| ┐Qt’ | ┐Qt |

В третьем и четвертом тактах С:=1, J:=1, K:=1 и в соответствии с таблицей истинности дважды устанавливаются в противоположное состояние оба триггера. В третьем такте Q’:=0 и Q:=0, а в четвертом такте Q’:=1 и Q:=1. В пятом такте J:=0 , K:=1 и оба триггера устанавливаются в нуль. Наконец, в последнем такте С:=1, J;=1, K:=1 состояние обоих триггеров снова изменяется на противоположное Q’:=1, Q: =1.

Счетчики

Счетчик – многоразрядный ФУ, предназначенный для подсчета количества импульсов, поступающих на его вход. Схемы счетчиков разнообразны, и их можно классифицировать по нескольким признакам:

1) в зависимости от системы счисления, в которой ведется подсчет числа импульсов, на: а) двоичные; б) двоично-десятичные;

2) по способу организации переноса между разрядами счетчика: а) с последовательным переносом, б) параллельным переносом, в) групповым переносом;

3) в зависимости от арифметической операции, выполняемой счетчиком: а) суммирующие, б) вычитающие, в) реверсивные;

4) по способу управления: а) асинхронные, б) синхронные.

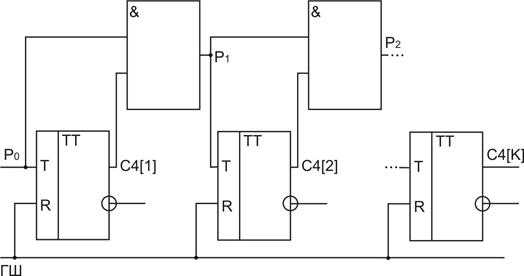

10.3.1 Счетчик с последовательным переносом

Рис.10.6. Двоичный суммирующий счетчик с последовательным переносом асинхронного типа.

На рис.10.6 и 10.7 приведены схема и УГО двоичного суммирующего счетчика с последовательным переносом асинхронного типа.

Рис.10.7. УГО счетчика

Ниже показана МОДИС- модель этого счетчика и временная диаграмма работы счетчика (рис.10.8).

Составим МОДИС- модель этого счетчика.

Описание переменных

‘ЗАВИСИМ’ С4 [1:K], Р [1: 2];

‘ИНЕЗАВ’ Р0, ГШ;

Описание схемы

С4 [1] ’:=‘ ‘ЕСЛИ’ ГШ ‘ТО’ 0

‘ИНЕСЛИ’ Р0 ‘ТО’ IC4 [1]

‘ИНАЧЕ’ C4 [1];

Р1 ‘:=‘ C4 [1] * P0

С4 [1:K] ‘:=‘ ‘ЕСЛИ’ ГШ ‘ТО’ 0

‘ИНЕСЛИ’ Р0 ‘ТО’ C4 [1:K]+1

“ИНАЧЕ’ C4 [1:K];

Рис. 10.8. Временная диаграмма работы счетчика

Каждый разряд счетчика делит частоту поступающих на его вход импульсов на 2. У асинхронного счетчика моменты срабатывания

отдельных разрядов счетчика определяются реальными задержками в схемах формирования переноса.

τp — время формирования переноса в одном разряде.

Быстродействие счетчика определяется временем пробега переноса по всем разрядам.

Трег= n * τp – время регистрации – интервал времени от момента поступления на вход счетчика очередного импульса до момента, когда новое значение установится во всех разрядах счетчика.

n –количество разрядов в счетчике.

10.3.2. Счетчик с параллельным переносом

Как следует из рис. 10.9. счетчик является синхронным, так как срабатывание всех триггеров происходит практически одновременно при поступлении на его вход сигнала Р0 . Схемы формирования переносов строятся по следующим формулам:

Р1 ‘:=‘ Р0 * Q1;

Р2 ‘:=‘ P1 * Q2 = P0 * Q1 * Q2;

…Pк ‘:=’ P0 * Q1 * Q2 * … * Qk-1; Трег≈ τp.

Счетчики с параллельным переносом обладают наибольшим быстродействием, причем Трег теоретически не зависит от количества разрядов. Однако на практике такие счетчики строятся не более, чем на 8 разрядов.

Рис. 10.9. Счетчик с параллельным переносом

infopedia.su

Двухтактный ( двухступенчатый) D-триггер

D — триггер можно выполнить двухступенчатым.

Первая ступень представляет собой одноступенчатый D-триггер, а вторая — синхронный RS-триггер.

На схемах двухтактный D- триггер обозначается следующим образом.

Рис. 0.21

Принцип действия двухтактного D- триггера основан на принципе действия RS триггера с динамическими входами. Т.е. первая ступень переключается по переднему фронту тактового импульса, вторая по его срезу.

Схема двухтактного D- триггера имеет следующий вид.

Рис. 0.22

Работа двухтактного D- триггера наглядно отражена в описании его принципа работы

Так же как и в одноступенчатом D-триггере в 2-х ступенчатой схеме возможно реализовать функцию valve. В результате получим универсальный 2-х ступенчатый DV-триггер.

Рис. 0.23

Условное обозначение такого триггера имеет следующий вид:

Рис. 0.24

Двухступенчатый D-триггер получил широкое применение из-за его универсальности. Так, например, если соединить с D входом, то с каждым синхроимпульсом будет меняться потенциал на входе D и, следовательно, состояние триггера. Таким образом, получается счетный Т-триггер.

Рис. 0.25

Кроме того, на базе таких триггеров можно реализовать и другие виды триггеров.

Развитие универсальных триггеров происходит в связи с необходимостью экономии средств при проектировании и изготовлении радиоэлектронной аппаратуры.

Реальные микросхемы функционально являющиеся D -триггерами обозначаются следующим образом: ТМ. Так, например, микросхема 155ТМ2 является D-триггером.

Итак D-триггеры, цифровые устройства со счётным запуском, и не имеющие запрещённых комбинаций сигналов, подаваемых на их информационные входы.

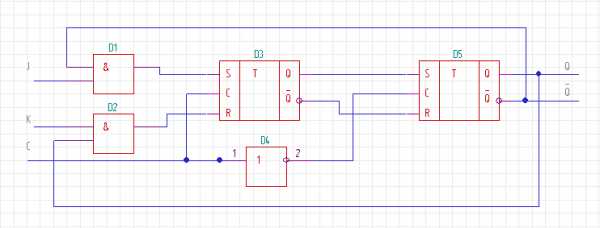

JK-триггеры.

JK-триггер –это триггер с двумя сигнальными и одним синхронным входами.

Такие триггеры часто называются универсальными, так как на их основе можно получить RS- и T-триггеры.

Название выводов у таких триггеров пошло от английских слов jerh -резкий толчок, kill — убить

Назначение- JK-триггеров универсальное.

Выполняется JK-триггер по двухступенчатой схеме с использованием основного и вспомогательного RS-триггера соединённых последовательно и имеющих обратную связь..

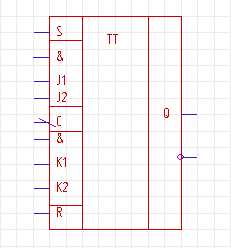

JK-триггеры получили следующее условное обозначение:

Рис. 0.26

Микросхемы JK-триггеров имеют обозначение ТВ. Например JK-триггер исполненный в комплекте микросхем 555 серии имеет обозначение — 555ТВ9.

Информационные входы J и K аналогичны входам S и R тактируемого RSC- триггера.

Принцип действия JK-триггеров аналогичен RSC триггеру, но JK-триггеры не имеют запрещающей комбинации. Т.е. во время действия тактового импульса сигнал записывается в основной триггер, а в момент окончания сигнал считывается вспомогательным RS-триггером.

Схема JK-триггеров.

Рис. 0.27

Рис. 0.27

На схеме, представленной выше, входы J, K являются информационными входами. Они аналогичны S и R входам тактируемого RSC-триггера (R эквивалентен K входу, S — J входу).

Работу (изменение состояний) JK — триггера при С=1 можно представить в виде следующей таблицы.

| Jn | Kn | Qn+1 |

| Qn | ||

При J=1, К=0 по срезу тактового импульса триггер устанавливается в единичное состояние, т.е. Q=1.

При J=0, К=1 — переключается в нулевое состояние, т.е. Q=0.

При J=0, К=0 — хранит раннее записанную информацию.

В данном триггере так же возможно осуществление счётного режима. Сказанное происходит при J=К=1. Триггер переключается каждым счетным импульсом приходящим на вход С..

Рассмотрим работу JK — триггера более подробно.

При J=K=0 на выходах DD1 и DD2 устанавливаются 1, которые для триггеров с инверсными входами являются пассивными сигналами. Следовательно, триггер Т1 и JK — триггер в целом своего состояния не изменяет.

Чтобы на выходе DD1 появился 0, необходимо чтобы J=1, C=1, =1. Тогда триггер Т1 переходит в 1 состояние, а по срезу тактового импульса и триггер Т2 переходит в 1. Следовательно, Q2=1.

При К=1, С=1, Q=1 на выходе DD2 появляется 0, переводящая триггер Т1 в нулевое состояние, а по срезу триггер Т2 в 0 и, следовательно, JK — триггер в целом переходит в нулевое состояние (Q=0, =1).

В отличие от RSC — триггеров одновременное присутствие единицы на сигнальных входах JK не является запрещающей комбинацией. При этом JK — триггер работает в счетном режиме, т.е. переключается спадом каждого тактирующего импульса.

На базе JК — триггеров можно построить любой из ранее рассмотренных.

Похожие статьи:

poznayka.org

Триггер — Национальная библиотека им. Н. Э. Баумана

Материал из Национальной библиотеки им. Н. Э. Баумана

Последнее изменение этой страницы: 17:36, 7 января 2015.

Триггер — это запоминающее устройство, хранящее одно из двух состояний — либо 0 либо 1.

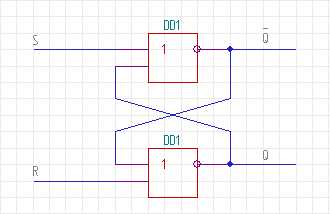

RS — триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

Рис. 1.1. RS-триггер с прямыми информационными входами.S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Рис. 1.2. RS-триггер с инверсными информационными входами.Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

Рис. 1.3. Классическая реализация RS-триггера.

Рис. 1.3. Классическая реализация RS-триггера.Таблица истинности:

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 0 | 0 | 0 | 0 | 1 | режим хранения нуля |

| 0 | 0 | 1 | 1 | 0 | режим хранения единицы |

| 1 | 0 | 0 | 1 | 0 | установка в состояние 1 |

| 1 | 0 | 1 | 1 | 0 | режим хранения 1 |

| 0 | 1 | 0 | 0 | 1 | режим хранения нуля |

| 0 | 1 | 1 | 0 | 1 | сброс в ноль |

| 1 | 1 | 0 | 0 | 0 | запрещено |

| 1 | 1 | 1 | 0 | 0 | запрещено |

Когда оба входа активны, то Q=Q¯=0{\displaystyle Q={\overline {Q}}=0}. Но, по определению, они противоположны ⇒R=S=1⇒{\displaystyle \Rightarrow R=S=1\Rightarrow } запрещенное состояние, но оно однозначно определено. Эта особенность используется для ускорения переключения схемы.

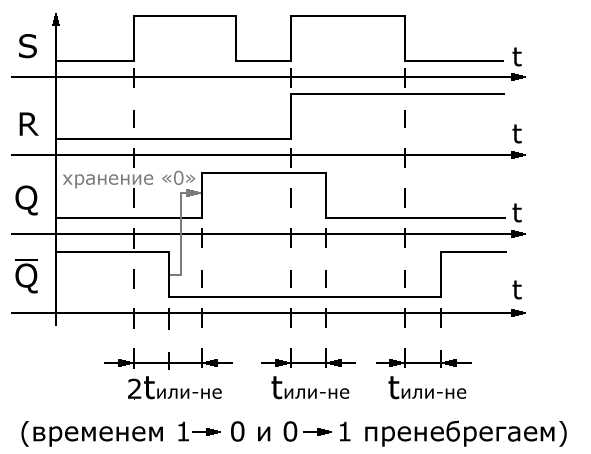

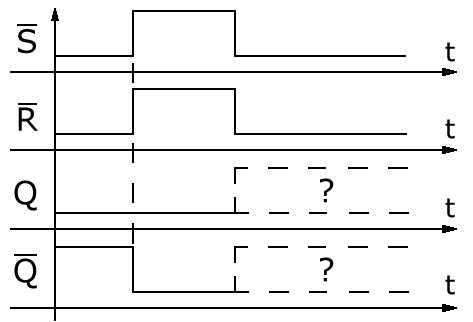

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Рис. 1.4. Временные диаграммы RS-триггера.

Рис. 1.4. Временные диаграммы RS-триггера.Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Рис. 1.5. Использование RS-триггера в качестве генератора случайных чисел. Рис. 1.6. Временные диаграммы

Рис. 1.6. Временные диаграммыДругая реализация RS-триггера

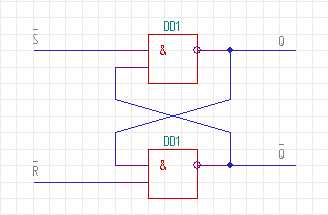

Также RS-триггер можно реализовать на базе элеметов «И-НЕ» (рис. 6). Входы у такой реализации — инверсные.

Рис. 1.7. Реализация RS-триггера на базе элементов «И-НЕ».

Рис. 1.7. Реализация RS-триггера на базе элементов «И-НЕ».Синхронный RS-триггер

Добавляется вход синхронизации С (основное отличие от асинхронных триггеров, описанных выше). Логика работы — активный вход синхронизации разрешает работу триггера. При неактивном входе синхронизации триггер не реагирует на входные значения. То есть:

- C=0; R,S — любые. Q(t+1)=Q(t)

- C=1

- R=S=0 — хранение

- S=0 R=1 — сброс (установка нуля)

- S=1 R=0 — установка единицы

- S=1 R=1 — запрещенное состояние

Схема синхронного RS-триггера

Рис. 2.1. Схема реализации синхронного RS-триггера.Синхронный JK-триггер

Основное преимущество данного триггера — у него нет запрещенного состояния.

Рис. 3.1. Условное обозначение синхронного JK-триггера.Логика работы:

- C=1

- J=0 K=1 Q(t+1)=0

- J=0 K=0 Q(t+1)=Q(t)

- J=1 K=0 Q(t+1)=1

- J=1 K=1 Q(t+1)=no Q(t)

- C=0 — режим хранения

Схема JK-триггера

Рис. 3.2. Схема JK-триггера и временные диаграммы его работы.

Рис. 3.2. Схема JK-триггера и временные диаграммы его работы.  Рис. 3.3. Временные диаграммы.

Рис. 3.3. Временные диаграммы.Считается, что значения на выходе изменяются одновременно. Записать в триггер можно только изменяющееся значение, хранимое в триггере значение — нельзя.

Конкретная реализация синхронного JK-триггера

Рис. 3.4. Конкретная реализация JK-триггера и временные диаграммы его работы.

Рис. 3.4. Конкретная реализация JK-триггера и временные диаграммы его работы.  Рис. 3.5. Временные диаграммы.

Рис. 3.5. Временные диаграммы.Если длительность управляющих сигналов больше времени переключения триггера — получаем автоколебательный режим (при наличии двух единиц на входах).

При J=K=1{\displaystyle J=K=1\,\!} необходимо подать на вход сихронизирующий импульс, не превышая время переключения (время ПП) внутри JK-триггера.

tJK=2tNOR+tAND{\displaystyle t_{JK}=2t_{NOR}+t_{AND}\,\!}

Окончание автоколебательного процесса определяется длительностью сигнала синхронизации и времени установки триггера.

D-триггер

Является синхронным триггером

- если С=0, то Q(t+1)=Q(t) — режим хранения

- если С=1, то Q(t+1)=D

Таким образом триггер сохраняет значение поданное на вход D.

Рис. 4.1. Условное обозначение D-триггера, его реализация и временные диаграммы его работы. Рис. 4.2. Временные диаграммы.

Рис. 4.2. Временные диаграммы.При C=0{\displaystyle C=0} и R=S=1{\displaystyle R=S=1} возникает запрещенное состояние.

Предназначен для хранения мнформации на входе D{\displaystyle D} при C=1{\displaystyle C=1}

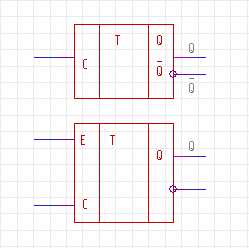

Т-триггер

Рис. 5.1. Условное обозначение T-триггера.

Рис. 5.1. Условное обозначение T-триггера.Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при какхи условиях).

Рис. 5.2. Схема T-триггера.

Рис. 5.2. Схема T-триггера.Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Может быть реализован и на синхронном RS-триггере (рис. 5.3).

Рис. 5.3. Реализация T-триггера на базе RS-триггера.Двухступенчатые триггеры

Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0).

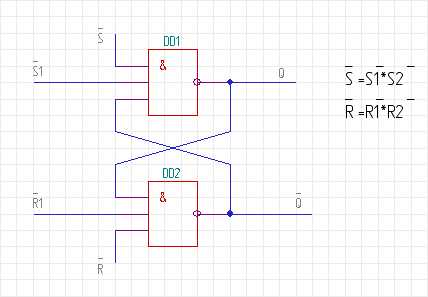

В основе — RS триггер.

Рис. 6.1. Общий вид двухступенчатых триггеров.Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации.

- 1-я ступень — ведущая (master).

- 2-я ступень — ведомая (slave).

Двухступенчатый синхронный RS-триггер

Рис. 6.2. Схема двухступенчатого синхронного RS-триггера.

Рис. 6.2. Схема двухступенчатого синхронного RS-триггера.Запись происходит по спаду (изменение с 1 до 0). Основа — два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме — см. рис 6.3).

Рис. 6.3. Условное обозначение двухступенчатого синхронного RS-триггера.Двухступенчатый D-триггер

Рис. 6.4. Схема и условное обозначение двухступенчатого D-триггера.

Рис. 6.4. Схема и условное обозначение двухступенчатого D-триггера.Логика работы та же что и у RS-триггера. С=1 — запись в первый триггер, С=0 — запись из первого во второй (запись по спаду).

Двухступенчатый JK-триггер

Рис. 6.5. Схема двухступенчатого JK-триггера.Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1{\displaystyle J=1K=1} и C=1{\displaystyle C=1} вознмкает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2й триггер, т.е. используются только внутренние обратные связи (ОС).

Для устранения этого недостатка можно модифицировать схему (рис. 6.6)

Рис. 6.6. Схема двухступенчатого JK-триггера (без автоколебательного процесса).

Рис. 6.6. Схема двухступенчатого JK-триггера (без автоколебательного процесса).Особенность схемы — наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записывыаются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна.

Приведенные выше (рис. 6.5 и 6.6) схемы являются базовыми, теперь следует рассмотреть конкретные реализации.

Рис. 6.7. Реализация двухступенчатого JK-триггера на базе элементов «И-НЕ».- D1-D2 — схема управления первой ступенью;

- D3-D4 — элементы памяти первой ступени; (D1-D4 в сумме — синхронный RS-триггер)

- D5-D6 — схема управления второй ступенью;

- D7-D8 — элементы памяти второй ступени; (D5-D8 в сумме — синхронный RS-триггер)

На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют «1» (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1{\displaystyle C=1}, либо при J=K=0{\displaystyle J=K=0}. Перезапись — при C=0{\displaystyle C=0} (на выходах D1 и D2 — единицы).

Еще эту схему можно получить на базе RS-триггеров (вывод схемы — на рис. 6.8)

Рис. 6.8. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).

Рис. 6.8. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).Универсальные триггеры

Рис. 7.1. Пример универсального триггера.При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 — они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример — рис 7.1, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи — приоритет у асинхронных входов.

Универсальный JK-триггер

Рис. 7.2. Обозначение универсального JK-триггера.

Рис. 7.2. Обозначение универсального JK-триггера.Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3хвходовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательнео, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется «1», если на всех J — «1». Для входа K ситуация аналогичная.

Ступенчатый D-триггер

Классическая схема ступенчатого D-триггера представлена на рисунке 8.1.

Рис. 8.1. Разработка ступенчатого D-триггера.

Рис. 8.1. Разработка ступенчатого D-триггера.Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

T3{\displaystyle T_{3}\,} — с инверсными входами (рем хранение — оба значения равны «1»). Если C=0{\displaystyle C=0\,}, то T2=T3=1{\displaystyle T_{2}=T_{3}=1\,}, то есть при C=0T3=1{\displaystyle C=0T_{3}=1\,}, а при C=1{\displaystyle C=1\,} T3{\displaystyle T_{3}\,} определяется тем, что подается на вход D.

При C=0,D=0{\displaystyle C=0,D=0\,} в T1{\displaystyle T_{1}\,} записывается некоторое значение, а T2{\displaystyle T_{2}\,} находится в запрещенном состоянии (две «1»).

Если при C=1{\displaystyle C=1\,} T2=1{\displaystyle T_{2}=1\,} и T3=0{\displaystyle T_{3}=0\,}, то произойдет переход в режим записи и проихойдет запись «0» во вторую ступень.

Рассмотрим случай, когда C=0,D=1{\displaystyle C=0,D=1\,}. Пусть D4=0{\displaystyle D4=0\,}, вход D4=0{\displaystyle D4=0\,}, тогда D1=1{\displaystyle D1=1\,}, можно наблюдать противоположную картину: T2{\displaystyle T_{2}\,} находится в режиме записи значения, а T1{\displaystyle T_{1}\,} — в запрещенном состоянии.

Рис. 8.2. Условное обозначение ступенчатого D-триггера.При переключении C из «0» в «1» на D3 происходит то же изменение, что и на D2 — переход из 1 в 0. Тогда T3{\displaystyle T_{3}\,} находится в режиме записи логической единицы:

(0)Q→1{\displaystyle (0)Q\rightarrow 1} (1)Q¯→0{\displaystyle (1){\bar {Q}}\rightarrow 0}При C=1{\displaystyle C=1\,} значение на входе D поменяется: 1→0{\displaystyle 1\rightarrow 0\,}, выход D4 установится в значение логической «1», поэтому D1{\displaystyle D1\,} станет равным 1 (его значение на выходе не меняется, на D2 — то же самое (только там — логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2).

При C=1{\displaystyle C=1\,} значение на входе D изменяется в порядке 1→0→1{\displaystyle 1\rightarrow 0\rightarrow 1\,}, значение D3 меняться не будет. Следовательно, при C=0{\displaystyle C=0\,} на выходе значение не будет меняться, при C=1{\displaystyle C=1\,} значение навыходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту).

- Первый триггер — для фиксации того, что хотим записать «0»;

- Второй триггер — для фиксации того, что хотим записать «1».

В итоге, при C:0→1{\displaystyle C:0\rightarrow 1} происходит запись, то есть переключение в другое состояние (или в запрещенное состояние).

Рис. 8.3. Преобразование ступенчатого D-триггера в универсальный.

Рис. 8.4. Условное графическое обозначение универсального D-триггера.

Рис. 8.3. Преобразование ступенчатого D-триггера в универсальный.

Рис. 8.4. Условное графическое обозначение универсального D-триггера.Можно сделать из данного триггера универсальный (рис 8.3). Для этого необходимо добавить асинхронные входы во вторую и первую ступени (для того, чтобы не получать запрещенное состояние только при наличии (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} во второй ступени). Устанавливаем (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} на D1 и D4, чтобы не изменять выход в режиме хранения (при C=0{\displaystyle C=0\,} — на D2 и D3). Условное изображение полученного триггера приведено на рисунке 8.4.

ru.bmstu.wiki

D – триггеры

D– триггеры имеет один информационный вход (D- вход) для установки в “1” или “0” и вход синхронизации С (происходит от словаdelay — задержка)

ОсобенностьD– триггеров:

Сигнал на входе Qв тактеt+ 1 повторяет входной

сигнал в предыдущем такте

в предыдущем такте и сохраняет (запоминает) это состояние

до следующего тактового импульса, т.

е.D– триггер задерживает

на один такт информацию, существовавшую

на входеD.

и сохраняет (запоминает) это состояние

до следующего тактового импульса, т.

е.D– триггер задерживает

на один такт информацию, существовавшую

на входеD.

Закон функционирования D– триггера:

Структурная схема D– триггера и условные значения

а) – со статическим управлением

б) – с динамическим управлением

Таблица истинности.

Такт t | Такт t+ 1 | ||

C |

|

|

|

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 1 |

При С = 0 состояние Тг устойчиво и не зависит от уровня сигнала на информационном входе D.

Сокращенная таблица

Такт t | Такт t+ 1 |

|

|

0 | 0 |

1 | 1 |

D– триггер можно образовать

из любого синхронногоRS- илиJK– триггера, если

на их информационные входы одновременно

подавать взаимно инверсные сигналыDи .

.

Хранение информации D– триггерами обеспечиваются за счет цепей синхронизации, поэтому все реальныеD– триггеры –тактируемые.

Управление может быть статическим, динамическим и двухступенчатым.

Временная диаграмма

Минимальный интервал времени между двумя тактовыми импульсами, при котором Тг работает без сбоев

Соответственно максимальная частота переключателей

Dv – триггеры

DV– триггер представляет собой модификациюD– триггера. Их логические функции определяются наличием дополнительного разрешающего входаV, играющего роль разрешающего по отношению ко входуD.

ПриV= 1 триггер работает какD– триггер

При V= 0 — переходит в режим хранения информации независимо от состояния входаD.

Управление функционированием DV– триггера имеет следующий вид:

Наличие V– входа расширяет функциональные возможностиD– триггера, позволяя в нужный момент времени сохранять информацию на выходах в течение нужного числа тактов.

Поскольку вход V– подготавливающий, сигналV= 1должен перекрывать по длительности оба фронта тактового импульса.

Наиболее удобны эти триггеры в быстродействующих схемах, поскольку передача информации происходит по одному входу, т. е. исключено состязание сигналов.Основные применения: запоминание информации в качестве разряда регистра или счетчика.

T – триггер (счетный триггер)

T– триггер имеет один информационныйT– вход (toggle- чека) и отличается простотой действия.

Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или отрицательном) перепаде напряжения на входе.

В сериях выпускаемых микросхем таких триггеров, как правило, нет. Но они могут быть созданы на базе других триггеров.

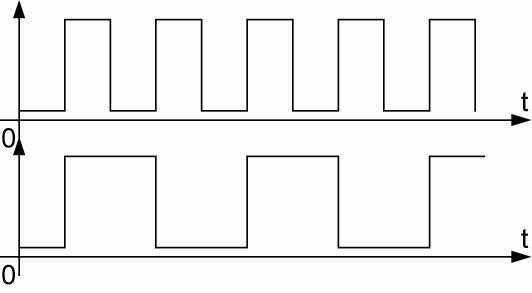

На основе D– триггера Временная диаграмма

T– триггер – единственный вид триггера, текущее состояние которого определяется не информацией на входах, а состояние в предыдущем такте.

Уравнение T– триггер имеет вид:

Как видно из временной диаграммы частота на выходе T– триггер в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Состояние счетных триггеров Сокращенная таблица состояний

T– триггер с прямымдинамическим управлением.

studfile.net